主要应用于要求有统一时间进行生产,调度的单位如:电力,机场、轻轨、地铁、体育场馆、酒店、医院、部队、油田、水利工程等领域。大区域时钟系统主要由母钟和多台子钟构成。

青州市和恩风机配件厂

青州市和恩风机配件厂

佛山市众齿健医疗器械有限公司

佛山市众齿健医疗器械有限公司

浙江海昕新材料科技有限公司

浙江海昕新材料科技有限公司

开平市水口镇古益卫浴厂

开平市水口镇古益卫浴厂

安阳金耀冶金有限公司

安阳金耀冶金有限公司

深圳市龙岗区盈旺美甲用品厂

深圳市龙岗区盈旺美甲用品厂

惠州市快乐人乐器有限公司

惠州市快乐人乐器有限公司

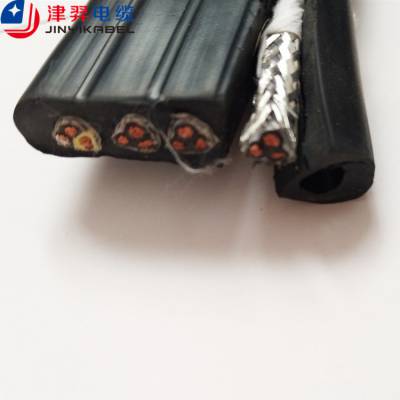

上海津羿电线电缆有限公司

上海津羿电线电缆有限公司

深圳市鑫永业五金制品有限公司

深圳市鑫永业五金制品有限公司

高阳县盛霞纺织品制造有限公司

高阳县盛霞纺织品制造有限公司